Todas las actualizaciones del subsistema IOMMU se enviaron esta semana para el kernel Linux 6.8 en desarrollo.

Quizás más interesante que este atractivo para los lectores Phoronix es la presencia de compatibilidad con Apple M1 USB4/Thunderbolt DART para el núcleo principal. Como lo explica el desarrollador de código abierto Sven Peter V Serie de parches:

«El chipset M1 SoC tiene una segunda variante que es ligeramente diferente al DART normal utilizado para los puertos PCIe USB4. Admite 64 flujos en lugar de 16, lo que requiere un ligero cambio en el diseño MMIO. Parece que no hay forma de distinguirlos de los DART normales con solo mirar el registro DART_PARAM, por lo que «Tenemos que agregarle un nuevo consenso».

DART es el IOMMU patentado por Apple conocido como tabla de resolución de direcciones del dispositivo y es necesario para que los periféricos Apple Silicon admitan DMA.

La compatibilidad con Apple M1 USB4/Thunderbolt DART se alinea con otros esfuerzos recientes de soporte de hardware realizados por el equipo de Asahi Linux para mejorar la compatibilidad con Linux en Apple Silicon.

Otro trabajo importante con el pull de Linux 6.8 IOMMU es un conjunto de parches de AMD para mejorar la lógica de invalidación TLB de su controlador IOMMU. Actualmente, el controlador está invalidando una sola página o un rango completo de E/S para el dominio especificado. Sin embargo, los dispositivos AMD IOMMU son capaces de admitir la invalidación de varias páginas. Con los parches de Linux 6.8, ahora se admite la invalidación de una serie de páginas. Por lo tanto, el controlador AMD IOMMU ahora es bueno para invalidar múltiples páginas de invitados en lugar de solo una página o todo el rango de un único espacio de direcciones.

el Retiro de IOMMU También contiene varias actualizaciones del controlador ARM SMMU, limpió y refactorizó el código para el controlador Intel VT-d, y el controlador Virt IOMMU ahora puede manejar transmisiones de E/S TLB diferidas. La limpieza diferida en la ruta VirtIO IOMMU puede resultar en «Aumento significativo del rendimiento en comparación con una ventana durante la cual los dispositivos aún pueden acceder a la memoria IOMMU previamente asignada cuando arrancan con CONFIG_IOMMU_DEFAULT_DMA_LAZY.«

«Food ninja. Freelance fanático de la cultura pop. Wannabe zombie maven. Aficionado a Twitter».

More Stories

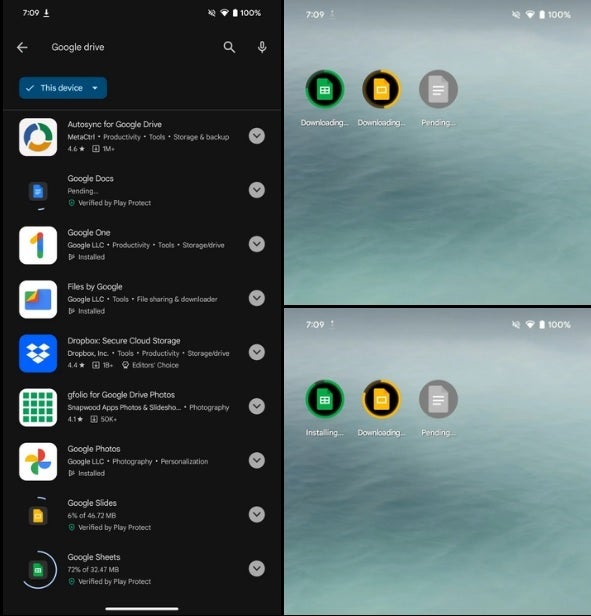

Ahora se pueden descargar dos nuevas aplicaciones desde Play Store e instalarlas en su teléfono Android simultáneamente

La imagen filtrada de la serie iPhone 16 muestra cuán masivo es el iPhone 16 Pro Max

7 atajos de teclado de Google Docs para hacer más en menos tiempo